2016-12-04 10:48:41

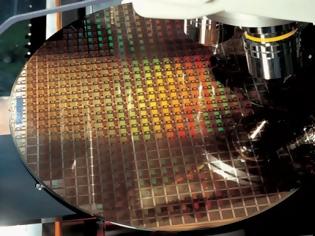

Σε μια προσπάθεια να γεφυρώσει το χάσμα μεταξύ 16nm FinFET και 10nm FinFET μεθόδων κατασκευής, αλλά ταυτόχρονα και για να αποκτήσει ένα ανταγωνιστικό πλεονέκτημα απέναντι στις Samsung και GlobalFoundries, η TSMC ετοιμάζεται να ανακοινώσει μια νέα μέθοδο κατασκευής των 12nm.Η νέα αυτή μέθοδος, αρχικά αναμενόταν να παρουσιαστεί ως η τέταρτη βελτιστοποιημένη έκδοση της μεθόδου κατασκευής των 16nm FinFET, με την TSMC να διαθέτει ήδη τρεις μεθόδους, τόσο για υψηλών επιδόσεων τσιπ, όσο και για ιδιαίτερα χαμηλής κατανάλωσης, που μπορούν να λειτουργήσουν ακόμα και με λιγότερο από 0,6V. Η νέα μέθοδος αναμένεται να προσφέρει χαμηλότερο leakage και καλύτερα χαρακτηριστικά από οικονομικής άποψης, για τους πελάτες της εταιρίας. Επιπλέον του ανταγωνιστικού πλεονεκτήματος έναντι των Samsung και GlobalFoundries, η νέα μέθοδος κατασκευής θεωρείται ότι θα είναι ιδιαίτερα ανταγωνιστική έναντι και παλαιότερων μεθόδων κατασκευής, των 28nm ή νεώτερες.

Παράλληλα θα δώσει την δυνατότητα σε εταιρίες που δεν έχουν την οικονομική δυνατότητα να σχεδιάσουν τσιπς κατάλληλα για την μέθοδο κατασκευής των 10nm, να χρησιμοποιήσουν την νέα αυτή μέθοδο κατασκευής ως ενδιάμεσο βήμα. Τέλος, να αναφέρουμε ότι και η GlobalFoundries έχει ανακοινώσει από την μεριά της μέθοδο κατασκευής των 12nm πριν λίγο καιρό. Πρόκειται όμως για planar μέθοδο και όχι FinFET, η οποία χρησιμοποιεί τεχνολογία Fully Depleted Silicon-On-Insulator (FD-SOI). Η GlobalFoundries ισχυρίζεται ότι η νέα της αυτή μέθοδος, θα είναι σε θέση να προσφέρει 15% υψηλότερες επιδόσεις, 50% μικρότερη κατανάλωση και με μικρότερο κόστος έναντι των υπαρχόντων μεθόδων κατασκευής των 16nm FinFET.

Freegr network blog- News about pc, technology.

freegr

Παράλληλα θα δώσει την δυνατότητα σε εταιρίες που δεν έχουν την οικονομική δυνατότητα να σχεδιάσουν τσιπς κατάλληλα για την μέθοδο κατασκευής των 10nm, να χρησιμοποιήσουν την νέα αυτή μέθοδο κατασκευής ως ενδιάμεσο βήμα. Τέλος, να αναφέρουμε ότι και η GlobalFoundries έχει ανακοινώσει από την μεριά της μέθοδο κατασκευής των 12nm πριν λίγο καιρό. Πρόκειται όμως για planar μέθοδο και όχι FinFET, η οποία χρησιμοποιεί τεχνολογία Fully Depleted Silicon-On-Insulator (FD-SOI). Η GlobalFoundries ισχυρίζεται ότι η νέα της αυτή μέθοδος, θα είναι σε θέση να προσφέρει 15% υψηλότερες επιδόσεις, 50% μικρότερη κατανάλωση και με μικρότερο κόστος έναντι των υπαρχόντων μεθόδων κατασκευής των 16nm FinFET.

Freegr network blog- News about pc, technology.

freegr

ΜΟΙΡΑΣΤΕΙΤΕ

ΔΕΙΤΕ ΑΚΟΜΑ

ΣΧΟΛΙΑΣΤΕ